SEMICONDUCTOR INDUSTRY NEWS Q4 2025 semiconductor update: AI packaging delays, power component supply stabilizes

Related Vendors

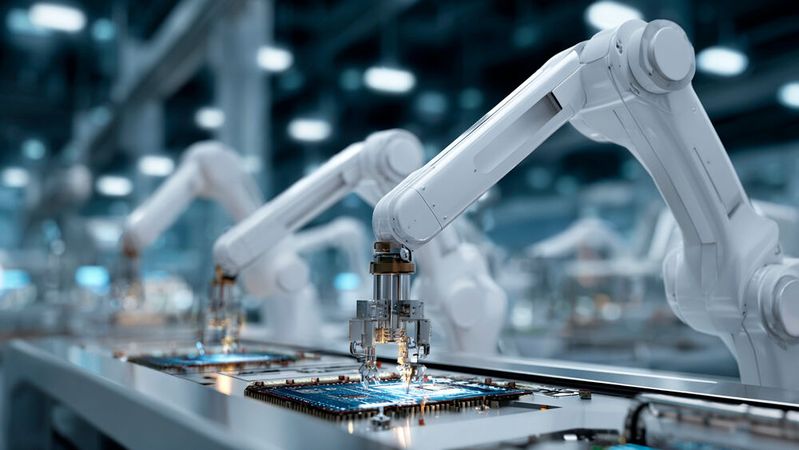

In Q4 2025, the semiconductor market split into two distinct realities. While analog and power IC supply largely normalized across industrial, automotive, and IoT segments, backend capacity and memory remained persistent bottlenecks. Surging AI compute demand continued to strain advanced packaging and DRAM supply, reinforcing structural constraints across the silicon value chain.

In the final quarter of 2025, the semiconductor industry entered a split reality. For most embedded and industrial designs, especially those dependent on power discretes, gate drivers, and analog sensors, lead times were stable, and inventories had largely returned to pre-pandemic norms. Automotive and IoT customers reported regular availability of standard voltage regulators, diodes, and power MOSFETs, even as some shifted focus to right-sizing inventory after the overordering cycles of 2022–2023.

At the same time, AI compute demand continued to outpace manufacturing throughput in several key areas, particularly in advanced packaging and memory. High-voltage substrate constraints in Chip-on-Wafer-on-Substrate with Large interposers (CoWoS-L), and persistent undersupply of high-bandwidth memory, extended allocation conditions for data center and accelerator customers.

DRAM pricing, driven by both AI buildout and capacity reallocation, climbed into Q1 territory. Some of these developments have begun to affect systems where power electronics interface with compute, storage, and signal-processing infrastructure.

Foundries including TSMC and OSATs like ASE responded with incremental capacity, and memory suppliers outlined multi-year capex plans. But the net effect in Q4 was a reinforcement of earlier dynamics: analog and power ICs saw normalization, while advanced silicon supply chains remained constrained by physical and geopolitical ceilings.

:quality(80)/p7i.vogel.de/wcms/e2/d6/e2d6eadc2e131f89909e587e7ff0f0c5/0126751999v2.jpeg)

CHIP INDUSTRY

A seismic shift in the world’s top ten chip maker rankings

Power Analog Supply Steadies, but Legacy Nodes Wind Down

Power semiconductors showed broad signs of normalization. Device families that had been heavily constrained during the pandemic, including gate drivers, high-voltage MOSFETs, bridge rectifiers, and digital isolators, were routinely available in Q4. Lead times for 60 V-650 V MOSFETs stabilized across most distributors, and parts in SOT-23 and DPAK packages were again available without allocation notices. NXP, Microchip, and Texas Instruments all reported industrial softness driven not by supply, but by conservative inventory management and slow recovery in some end markets.

Several suppliers noted sequential revenue declines in power and analog portfolios through Q3 and Q4. These were driven by inventory digestion, particularly in Europe and North America, where Tier 1s had overstocked key voltage regulators and control ICs during the shortage years. The downcycle gave fabless and IDMs room to rebalance packaging capacity and resume EOL planning for older devices.

However, availability should not be conflated with long-term stability. Foundries including TSMC, UMC and GlobalFoundries continued to transition backend packaging resources away from legacy analog and discrete lines. Devices still dependent on 180nm and 130nm nodes, especially in LDOs and voltage monitoring, are seeing last-time-buy programs as fabs prioritize more lucrative mixed-signal or RF designs.

While analog and discretes exited crisis mode, system designs depending on AI compute remained constrained by backend limitations. In Q4, Nvidia's flagship GB200 GPUs, built on the Blackwell architecture, faced shipment ceilings not due to wafer availability, but due to packaging bottlenecks at TSMC.

CoWoS-L lines, which support high-interconnect-density modules pairing GPUs with stacks of HBM, were again fully booked through the end of the year. Unlike conventional power or mixed-signal packaging, CoWoS-L requires large silicon interposers, tighter substrate tolerances, and thermal budgets that push substrate selection into high-end materials, often used in advanced power modules.

TSMC’s CEO confirmed in Q4 that CoWoS-L remained the single most constrained backend process in its entire manufacturing stack. Expansion programs in Chiayi and Kaohsiung are underway, with a projected monthly CoWoS output of 100,000 wafers by late 2026. However, most of this new capacity is already committed to Nvidia and hyperscaler customers. TSMC began offloading simpler assembly work to OSATs like ASE and SPIL to redirect internal tools to CoWoS-L packaging, further tightening availability for less advanced—but still margin-sensitive—power modules.

The substrate squeeze also affected some high-current DC-DC converters used in data center and automotive traction systems. With key OSATs prioritizing HBM and AI substrates, several packaging providers signaled longer cycle times for large-format copper-base laminate modules, a class of substrate used in high-power buck and boost converters. As AI server boards grow denser and thermals climb, some of these power stages are competing for space and material with the compute dies they support.

:quality(80)/p7i.vogel.de/wcms/d8/e0/d8e0676f168d0b5a2bf0f05d4b19f49b/0124415519v2.jpeg)

SEMICONDUCTOR INDUSTRY

What’s slowing the semiconductor boom? A view from the engineering front line

Memory Shortage Pushes DRAM into BOM-Sensitive Territory

The DRAM market, which had shown signs of recovery in mid-2025, fully flipped into shortage conditions by Q4. HBM3 and HBM3E allocations were sold out for both 2025 and 2026 at SK hynix, with Samsung close behind. Samsung’s 12-high 48 GB HBM3E modules entered production, but demand from Nvidia and other accelerator vendors far exceeded available packaging slots.

For the power electronics space, this would be distant noise, except for the reallocation effect it triggered. DRAM vendors shifted fab and packaging lines toward high-value HBM and DDR5 modules, accelerating end-of-life plans for DDR4. Micron halted new DDR4 quotes in September and ceased shipments on multiple lines by November. Samsung reversed a planned shutdown of its last DDR4 line only after direct customer intervention.

For industrial and embedded system designers still using DDR4-based control and signal-processing SoCs — often found in drives, inverters, and power metering devices — this realignment introduced new risks. Multiple board vendors reported 20-30% spot price increases for ECC and low-profile DDR4 modules during Q4, and availability for industrial temperature grades tightened sharply. Power systems with compute overlays or high-speed buffering, like energy gateway controllers or wide-bandgap inverter control boards, are now exposed to DRAM lead time volatility for the first time since 2021.

Policy Shifts Impact Mature and Mixed-Signal Flows

The geopolitics of chip supply saw renewed developments in Q4. In Europe, the Dutch government moved to assert control over Nexperia, citing national security and ownership concerns. Nexperia, a key supplier of automotive-grade discretes, voltage regulators, and ESD protection devices, saw its China-based manufacturing exports temporarily blocked by Beijing in retaliation. Although shipments resumed after negotiation, the incident raised new concerns about single-source sourcing for core passive and discrete parts. Several Tier 1s with high Nexperia exposure began evaluating second-source equivalents from Littelfuse and Diodes Inc.

In the U.S., a tariff-based workaround emerged for AI chip exports to China. The Trump administration announced that limited exports of Nvidia’s H200 accelerators could resume under license, with an additional 25% tariff. While this affects high-end compute, it also introduces indirect complexity for U.S.-built DC-DC power modules designed to accompany these GPUs in system reference designs. Nvidia’s board partners have indicated they are revisiting some module BOMs to adapt to supply volatility and tariff-influenced region-specific SKUs.

Supply divergence between U.S.-compliant and China-specific AI modules is now creating more fragmented demand profiles for adjacent analog and power components. As boards are redesigned for separate firmware and power envelope requirements, system integrators may need to dual-source power ICs across platforms with incompatible thermal and voltage profiles.

:quality(80)/p7i.vogel.de/wcms/38/4d/384d8b9a75b396da0399836b772d4941/0122507173v2.jpeg)

SEMICONDUCTOR INDUSTRY

Eighteen new semiconductor fabs to start construction in 2025

2026 Outlook: Backend Relief Will Be Uneven

Looking toward H1 2026, CoWoS-L packaging remains the rate limiter for AI module delivery. ASE’s ramped capacity may contribute marginal relief, but most growth is backloaded toward late 2026. Substrate suppliers are also playing catch-up, and ABF shortages could again impact high-end power module packaging, particularly in high-voltage or high-layer-count designs used in data center and EV power delivery.

On the analog side, inventories remain strong, and pricing is stable for core power IC families. But product teams tied to legacy 200 mm processes or DDR4-compatible memory subsystems will need to accelerate redesigns. With foundries pushing legacy lines toward sunset, power systems built on decade-old nodes or discontinued RAM types may see availability degrade faster than expected.

DRAM and NAND pricing will likely remain elevated through mid-2026, with DDR5 migration accelerating. For power products embedded within server or storage systems — such as point-of-load converters, battery management, or SSD power conditioning — this shift may alter thermal and BOM constraints even before silicon itself becomes scarce.

Q4 confirmed that most power and analog supply has stabilized. But with advanced packaging and HBM demand shaping foundry and OSAT behavior, ripple effects continue to reach beyond AI. As 2026 begins, backend constraints are dictating more than just compute module throughput; they are quietly reshaping the cost, availability, and longevity of the power systems that surround them.

(ID:50660365)

:quality(80)/p7i.vogel.de/wcms/55/5b/555bb8759d60243792dd736b86585f29/0130909253v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/db/75/db7507346cd4842ca5eb8838f45861ce/0130908924v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/44/0f/440f92984dc6c58eec920824ef55b54c/0130740285v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/be/dc/bedc263ae2b17f59ef71bfc822b95d27/0130740269v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/71/74/71744e9858925f4aae140ab39723ebf4/0131064963v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/8a/2a/8a2a43ba86d8fbb6089aa249a066e1f5/0131041579v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ea/60/ea600a89db0dc673ba3b6eb1ca56093e/0130736129v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/8b/ae/8bae28ce8ab5e6820bc036ce49939261/0130655531v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ef/3f/ef3f0ba1427bb0be71ae9a57274d5687/0131065708v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ac/3d/ac3d3fe7d72fdf885988709ea060c4af/0131062566v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/73/f2/73f20bf3ae2ce460cfe9ed13411613dd/0130955570v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/aa/a3/aaa3c94040c99a7aafb263e839b9ab22/0130953280v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/34/4a/344a3dc5a19429cf6726b7f8f7e2ee32/0130109719v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/be/c8/bec8d43fc0ee73414274be44608b2970/0129748903v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/23/ee/23ee4a97790d6009dbfd7d9577ffa723/0129220424v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/3c/d1/3cd1cacbceb792ba63727199c61ca434/0127801860v2.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/63/c7/63c7da97be945/diotec.png)

:fill(fff,0)/p7i.vogel.de/companies/68/08/6808a2b3b6595/het-logo.jpeg)

:quality(80)/p7i.vogel.de/wcms/37/e5/37e51381f4f8c8b5fa547e66fa63a8c2/0126972536v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/73/1b/731b2a2ed1082e7a4bc6971b76566475/0125343087v2.jpeg)