COOLING SOLUTIONS Maximize Lifetime & Power Density in High Power Semiconductors Modules

Sponsored by

Power electronics must achieve higher power in smaller housings, boosting efficiency and reducing costs. SiC-MOSFETs can replace IGBTs but are pricier. Press pack-device approaches and active heat sinks can enhance IGBT designs, improving performance.

Comparing power modules and disc-style devices

The trend of increasing power density in power semiconductors is approaching physical limitations due to isolation requirements. To overcome these limitations, efficient heat extraction methods are essential. Direct liquid cooling combined with advanced chip and interconnection technology offers a promising solution. Shifting from classical isolated assemblies to non-isolated counterparts can increase power density by a factor of 10.

Higher power density results in increased losses per area and elevated temperatures, stressing interconnecting joints. This necessitates replacing soft-soldered connections with sintering for enhanced stability and longevity. Improved cooling is critical, as insulating DCB ceramics limit thermal transfer.

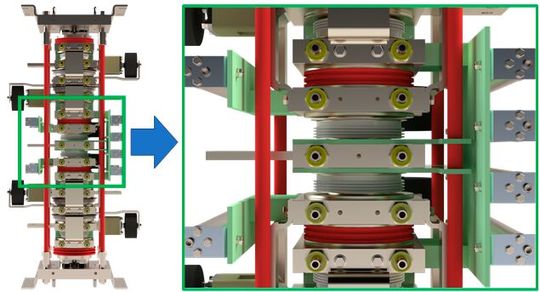

High-power disc devices, unlike power semiconductor modules, utilize electrically active cold plates for efficient cooling and material savings. Figure 1 depicts a typical power semiconductor module, while Figure 2 shows a stack assembly of a 2400 A / 4500 V 3-level phase-leg with active aluminum cold plates, which also serve as terminals and snubber circuit connection points. Efficient thermal management is achieved using non-conducting cooling liquids, such as a deionized water-glycol mixture.

Feasibility Study

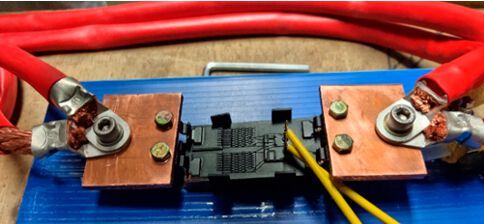

To enhance the thermal resistance by eliminating the direct copper bond (DCB) ceramics, 1200 V/200 A IGBT dies were directly soldered to a liquid-cooled plate. The initial approach utilized bond wires to connect components, leading to the first device under test (DUT), as shown in Figure 3. This 200 A IGBT die employed eight bond wires, each capable of handling 25 A, to link the emitters to the power terminals.

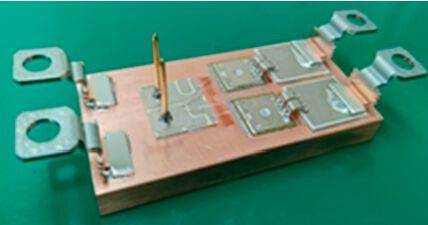

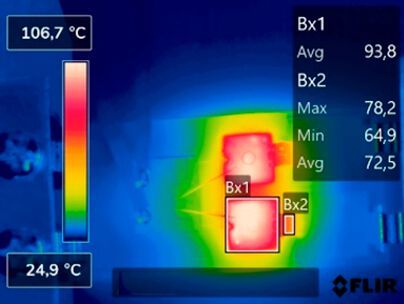

The DUT underwent testing with an infrared (IR) imaging setup, starting at 50 A and increasing in 50 A increments. At 200 A, the chip temperature rose by 70K, while the bond wires exceeded 400°C, as depicted in Figure 5. At 250 A, the bond wires fused, highlighting the limitations of this approach. Consequently, a new design was developed that used clip-soldered connections instead of bond wires, facilitated by a new solderable chip-metallization, as illustrated in Figure 6.

This new design showed significant improvement: at 200 A, the chip temperature reached 94°C, similar to the previous bond wire design. The clip's maximum temperature was 78°C, far below the bond wires' 400°C, as seen in Figure 7. The new design could handle currents exceeding 275 A before reaching an operating temperature of Tvj = 150°C.

An analysis of power loss density indicated that the setup could handle up to 380 W/cm2 at a temperature differential of 100 K, allowing a maximum current of 450 A for the new chip with a 2 cm2 area, and up to 250 A for the 150 A/183 mm2 standard die. These results reflect a marked improvement in thermal management and operational efficiency with the new design.

Electric testing

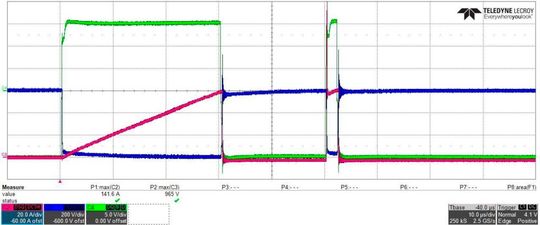

Though the main focus was thermal performance, electrical behaviour was tested. The double-pulse-test summarized in Figure 8 revealed sufficiently clean switching. Despite the non-optimized layout, the results were good enough for potential series development.

Cyclic load testing

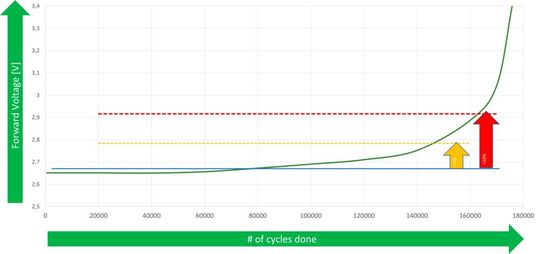

Power electronic components' lifetime is enhanced by outstanding thermal performance. As defined in IEC 60749, a power cycling test, or PCsec, was performed on the pad-and-clip assembly, which is expected to surpass bond-wire systems due to the elimination of bond-lift-off and bond-heel-crack issues. The test subjected several devices to these conditions, and despite the IGBT being rated at 150 A but burdened 250 A, the chips, in a single arrangement, lasted approximately 145,000 cycles before reaching a 5 % forward voltage increase as depicted in Figure 9. This performance is significantly better compared to 80,000 cycles for solder-bond technology, indicating potential for further improvements in chip metallization and solder alloys.

Conclusion

The omnipresent trend of increasing power density in power semiconductors as they are built today starts reaching physical limits due to the isolation requirement. To push these limits further, new methods to extract heat from power semiconductors more efficiently need to be identified.

One way of doing so is direct liquid cooling combined with a suitable chip- and interconnection technology as presented.

The shift from classical isolated assemblies to non-isolated counterparts opens the door to increase power density by a factor of 10, compared to today’s options.

PCIM Expo 2025: Join the industry highlight

Position your company at the forefront of the power electronics industry! Exhibit at the PCIM Expo 2025 in Nuremberg, Germany to showcase your solutions and connect with top decision-makers and innovators driving the industry forward.

Learn more

(ID:50379797)

:quality(80)/p7i.vogel.de/wcms/2f/f3/2ff3221bf7665de2d0acf83760bfd1fa/0130031523v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c3/16/c316e955a97f5d72d9678297b237b9e5/0129932858v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ef/0a/ef0adb0acf793fe147cc27c21f6a7a67/0129954238v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/53/f9/53f9301dfc9292d02960f7996c79cc6e/0129927601v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/6e/cd/6ecd41d095d5111cf4ed37b714844487/0129930878v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/02/c0/02c0e9722f70b1134dbf96fb59a9c73d/0129655179v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cc/67/cc670ea2029cd2af5c641af70e1bf734/0129816392v4.jpeg)

:quality(80)/p7i.vogel.de/wcms/ea/e6/eae6aee30071e67a5627027974437134/0129544613v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b1/5e/b15ee02b0ba02db70cf61e37d66ad1d3/0129349127v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/26/d5/26d591cc340077026eac56a0e7564faf/0129949603v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/4d/e0/4de02f76a37cbb3df30dd231de589c8e/0128866890v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/18/0b/180b7b63afc91e523592d8a5ce161c96/0129847487v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/be/c8/bec8d43fc0ee73414274be44608b2970/0129748903v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/23/ee/23ee4a97790d6009dbfd7d9577ffa723/0129220424v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/3c/d1/3cd1cacbceb792ba63727199c61ca434/0127801860v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/5a/a0/5aa0436498af618297961fd54ab36cdf/0126290792v2.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/60/4a/604a54b5ea863/lf-logo.png)

:quality(80)/p7i.vogel.de/wcms/b1/0a/b10a283cdf3e5f156781a7273c71a7e0/0129107484v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/f0/a4/f0a4ec50e99b87afad613593f0f0860b/0124997238v4.jpeg)