NEW PROJECT FastLane - Boosting EU material value chain for SiC power electronics

Related Vendors

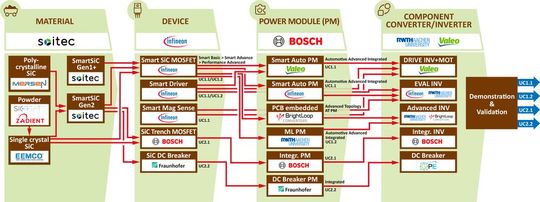

As the global electronics industry undergoes a seismic shift toward sustainability, efficiency, and sovereignty, Silicon Carbide (SiC) is emerging as the cornerstone of next-generation power electronics. At the heart of this transformation is FastLane—a three-year European funded project launched in 2024, uniting 29 partners across seven countries to redefine the SiC value chain from raw materials to system-level demonstrators.

Led by Valeo and supported by the EU, FastLane is more than a research project—it’s a strategic blueprint for Europe’s technological resilience. Its mission: to boost energy efficiency, reduce CO₂ emissions, and strengthen EU sovereignty. This article focusses on the key packaging material innovations such as metal ceramic substrates (silver free AMB), bonding wires, die top system and sinter paste. This project enables highly reliable, cost-effective and high performance SiC power modules.

The global electronics industry is undergoing a profound transformation, driven by the demand for higher efficiency, environmental sustainability, and strategic autonomy. In this evolving landscape, Silicon Carbide (SiC) has emerged as a key enabler of next-generation power applications. To harness its full potential, the European FastLane project, launched in 2024, supports EU independence in critical raw materials while developing an independent SiC raw material and device supply chain and broadening SiC functionalities to overcome current limitations

A Pan-European Effort to Reshape Power Electronics

FastLane is a three-year initiative co-funded by the European Union, bringing together 29 partners from seven countries, including leading research institutions, specialized SMEs, and major industrial players. Under the coordination of Valeo, the consortium aims to enhance energy efficiency and reduce the carbon footprint of power electronics by developing a robust, independent SiC supply chain—from raw materials to system-level demonstrators. By leveraging economies of scale, FastLane drives cost-efficient energy conversion applications, strengthening Europe's technological and economic resilience in power electronics.

The project’s comprehensive structure spans multiple work packages and collaborative efforts, covering the entire SiC power electronics value chain. This includes material development, device fabrication, packaging innovations, and final system integration.

Materials Innovation for Scalable SiC Integration

Within the FastLane consortium, materials development plays a central role in enabling the assembly and performance of advanced SiC power modules. Among the contributors, Heraeus Electronics supports the integration of six distinct SiC module designs through three specialized packaging technologies. These innovations address key challenges in thermal management, electrical performance, and reliability—critical factors for next-generation power electronics.

The company’s focus lies in developing environmentally responsible materials that facilitate miniaturization, forward integration, and high-efficiency energy conversion. In response to industry-wide shifts—such as the rise of e-mobility, AI, and next-generation communication technologies—collaborative innovation across the value chain has become essential. Heraeus Electronics engages in joint research efforts with academic institutions, start-ups, equipment providers, and end users, contributing to broader ecosystem development through EU funded initiatives and industry associations.

Technical Innovations: Three Packaging Building Blocks

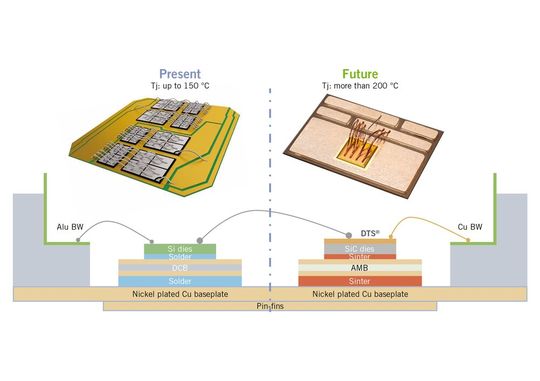

To achieve the FastLane project goal for higher efficiency of power modules SiC dies enable them to operate at >175 °C, with higher switching frequencies and increased power densities.

Their effective implementation requires advanced packaging materials. Heraeus Electronics contributes within FastLane with the following key innovations:

- 1. Ag sinter pastes enabling attachment of Active metal brazed (AMB) substrates without noble metal surfaces

- 2. Ag-free AMB substrates with designs reducing parasitic inductance and

- 3. Die-Top System (DTS©) enabling reliable Cu bonding to SiC dies.

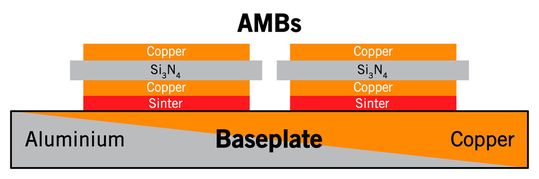

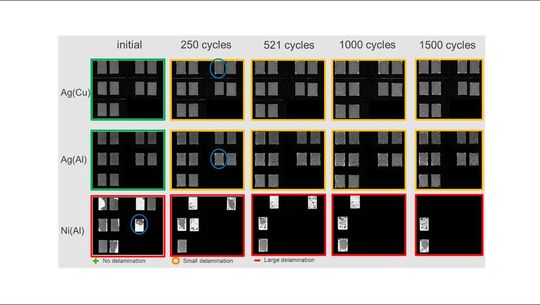

1. Silver Sintering for AMB Substrate Attachment on Aluminum Baseplates

To reduce both cost and weight in SiC power module packaging, Heraeus has developed the PE 360P silver sinter paste, enabling the attachment of Active Metal Brazed (AMB) substrates to aluminum baseplates without the need for precious metal surfaces.

This innovation offers significant advantages:

- Up to 70% weight reduction

- Cost savings of up to 91% compared to copper baseplates

Initial results with PE 360P show robust AMB adhesion and minimal delamination (<5%) already with Cu-coated Al baseplates after 1500 temperature cycles (–55 °C/+150 °C), comparable to similar Ag-coated baseplates. In contrast, Ni-coated Al baseplates fail to ensure sufficient adhesion.

Ongoing work focuses further on optimizing Ag sintering directly on non-precious metals coated Al.

This approach supports scalable, cost-efficient packaging for high-performance SiC modules.

2. Silver-Free, Low-Inductance AMB Substrates

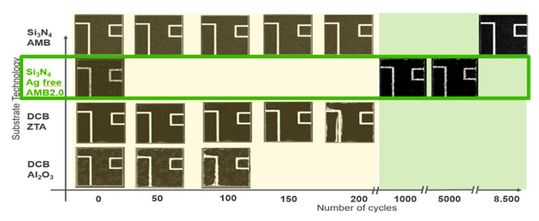

The second major innovation centers on the development of silver-free, low-inductance AMB substrates using Si3N4ceramics, designed to reduce parasitic inductance and improve cost efficiency.

Key benefits include:

- Reduced cost through elimination of silver (Ag content >60 wt% in conventional AMB pastes)

- Reduced Ag migration for enhanced reliability

- Superior performance compared to traditional Direct Copper Bonded (DCB) substrates

Scanning acoustic microscopy confirmed the reliability of these AMB 2.0 substrates after thermal shock testing (–65 °C to +150 °C). Their performance rivals Ag-containing AMB, surpasses DCB substrates, and meets all customer specifications. Their integration into Valeo’s low-inductance power modules is planned as the next step.

This innovation also strengthens the European AMB supply chain, with all key manufacturing partners—including metal and ceramic suppliers and Heraeus Electronics’ technology and production site—located within Europe. This supports risk mitigation, improves supply chain stability, reduces CO₂ emissions, and enhances the EU’s market position. To ensure secure global delivery capability, Heraeus Electronics also maintains a dual-source strategy in Asia.

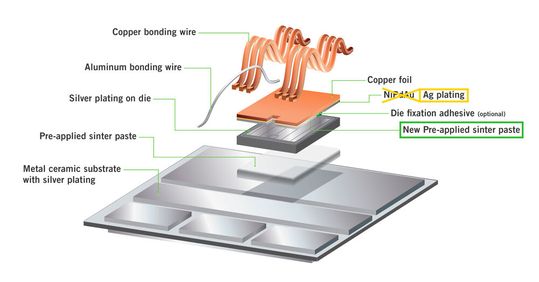

3. Die Top System for Copper Wire Bonding

The third building block addresses top-side interconnection, a critical factor for achieving high reliability in SiC modules. Heraeus has developed the Die Top System (DTS®) in collaboration with European partners. This system features a copper foil with pre-applied sinter material, enabling copper wire bonding with over 10× reliability improvement compared to aluminum bonding.

The industrialized DTS® Silver replaces NiPdAu metallization with Ag plating, ensuring:

- Simplified sintering

- Reliable copper bonding to SiC dies

Future development includes laser-structured DTS® Silver for finer wire bonding geometries (down to 0.5 × 0.5 mm²). These advanced interconnects will be evaluated in FastLane power modules for performance and reliability.

First-Year Deliverables and Ongoing Integration

In the first year of FastLane, Heraeus Electronics and its partners successfully delivered three core packaging innovations:

- Development of an Ag sinter paste for AMB attachment on Ag-metallized aluminum baseplates, replacing conventional copper

- Design of silver-free AMB substrates using Si3N4 ceramics for reduced cost and inductance

- Development of DTS® systems enabling reliable and cost-efficient copper wire bonding to SiC dies

These technologies are now undergoing integration and reliability testing across multiple power module use cases. This work will continue through June 2027, with the goal of enhancing SiC performance, efficiency, and resilience throughout Europe’s power electronics value chain.

Conclusion and Outlook: Tailored SiC Demonstrators for Strategic Applications

By integrating advanced SiC technologies into tailored demonstrators across mobility and energy domains, FastLane delivers on five major objectives:

It aims to reduce the environmental impact of power electronics by improving energy efficiency and lowering the carbon footprint of materials and processes. At the same time, it contributes to strengthening European sovereignty over critical raw materials by establishing a more independent and resilient SiC supply chain.

The project also focuses on unlocking new functionalities in SiC devices and packaging, enabling operation under higher temperatures, switching frequencies, and power densities. Cost optimization is pursued through innovations in materials and scalable manufacturing techniques. Finally, FastLane supports accelerated innovation in next-generation power electronics by fostering collaboration across research institutions, industrial partners, and technology developers. Ultimately improving usability and affordability for end users.

The contributions from all FastLane partners are enabling the development of SiC power module demonstrators tailored to specific end-user applications.

E-mobility:

- Light commercial vehicles (UCs 1.1 & 1.2a) for high-volume applications

- Ultra-class haul trucks (UC 1.2b) for high-power, heavy-duty environments

Energy systems:

- Power inverters for electrolyzers (UC 2.1) to support green hydrogen production

- Solid-state circuit breakers (UC 2.2) for grid protection and advanced battery storage

These demonstrators will validate the technical feasibility and performance of SiC modules under real-world conditions. Together, these efforts aim to position Europe at the forefront of sustainable, high-performance power electronics—powered by Silicon Carbide.

ACKNOWLEDGMENT:

(ID:50578840)

:quality(80)/p7i.vogel.de/wcms/55/5b/555bb8759d60243792dd736b86585f29/0130909253v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/db/75/db7507346cd4842ca5eb8838f45861ce/0130908924v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/44/0f/440f92984dc6c58eec920824ef55b54c/0130740285v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/be/dc/bedc263ae2b17f59ef71bfc822b95d27/0130740269v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ea/60/ea600a89db0dc673ba3b6eb1ca56093e/0130736129v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/8b/ae/8bae28ce8ab5e6820bc036ce49939261/0130655531v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/de/9b/de9beb17c1467fdb18301a114f31bf8e/0130651681v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/47/47/474773560a05ff45872e5942c2702e11/0130617850v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/07/89/0789a27b7dcc43dbdafd17f2b601e3a7/0130908474v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/9e/b0/9eb01567f828f28e7922897edc690be2/0130454119v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/db/bb/dbbb1b9c429bd4fc375a7937bb083ba1/0130804041v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/a3/30/a330337e234ac2000bb8829ce34ce001/0130871678v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/34/4a/344a3dc5a19429cf6726b7f8f7e2ee32/0130109719v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/be/c8/bec8d43fc0ee73414274be44608b2970/0129748903v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/23/ee/23ee4a97790d6009dbfd7d9577ffa723/0129220424v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/3c/d1/3cd1cacbceb792ba63727199c61ca434/0127801860v2.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/68/08/6808a2b3b6595/het-logo.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/5f/71/5f71d5f92a5f6/2000px-rogers-corporation-logo-svg.png)

:fill(fff,0)/p7i.vogel.de/companies/66/8b/668becd1c07eb/dowa-logo-word--1-.jpeg)

:quality(80)/p7i.vogel.de/wcms/9f/26/9f26e883a4087ed359f21694eb12c443/0127013676v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/f0/a4/f0a4ec50e99b87afad613593f0f0860b/0124997238v4.jpeg)